|

| Freq by 3 |

|

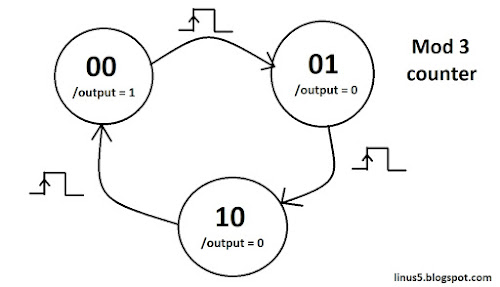

| FSM diagram for mod3 counter |

|

| freq by 3 dataflow |

|

| mod3 truth table |

VERILOG CODE

CODE OF D FLIPFLOP

module D_flipflop(D,CLK,SET,Q,Q_bar );

input D, CLK, SET;

output Q, Q_bar;

reg Q;

assign Q_bar = ~Q;

always @(posedge CLK or posedge SET)

begin

if (SET == 1'b1)

begin

Q = 1'b1;

end

else

begin

Q = D;

end

end

endmodule

CODE OF AND logic

module and_logic(

input a,

input b,

output out

);

assign out = a & b;

endmodule

CODE OF NOR logic

module nor_logic(

input a,

input b,

output out

);

assign out = ~(a | b);

endmodule

CODE of TOP logic:

module freqby_3(

input CLK,

input SET,

output Q

);

wire w1,w2,w3,w4,w5,w6,w7;

D_flipflop d2(.D(w1),.CLK(CLK),.SET(SET),.Q(w2),.Q_bar(w3) );

D_flipflop d1(.D(w4),.CLK(CLK),.SET(SET),.Q(w1),.Q_bar(w5) );

and_logic a1(.a(w5),.b(w3),.out(w4));

nor_logic n1(.a(w1),.b(w2),.out(w6));

D_flipflop d3(.D(w7),.CLK(w6),.SET(SET),.Q(Q),.Q_bar(w7) );

endmodule

Timing Waveforms

SIMMULATION:

0 comments:

Post a Comment