|

| NCO title |

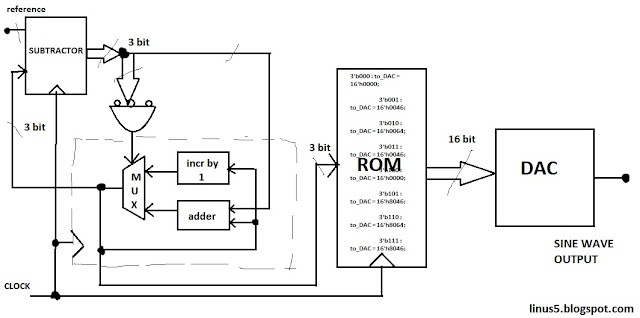

1. The NCO is the Numerically Controlled Oscillator which generates the signal wave digitally.

2. Signal generated here is discrete-timed & discrete-valued.

3. NCO takes the reference/frequency control word and does the phase accumulation.

4. The Phase accumulation is the addition of phase value(discrete/sampled one) at digital synchronous clock speed.

5. Phase Accumulator feeds the 16bit phase value from the Sine LUT(look up table) which is a ROM to the DAC.

6. DAC is the Digital to Analog Converter which generated continous timed & continous valued Sine Wave/signal.

7. The NCO is used widely in many communication related applications like wireless radio, digital- PLL's etc.

|

| NCO block |

|

| NCO data FLOW |

|

| NCO block level |

VERILOG CODE:

Phase accumulator Code:

module stage2_phaseAccumulator(ref,CLK,out_ROM);

input [2:0] ref;

input CLK;

reg [2:0] error_out;

reg [2:0] out_counter;

output [2:0] out_ROM;

assign out_ROM = out_counter;

initial

begin

error_out <= 3'b000;

out_counter <= 3'b000;

end

always @(posedge CLK)

begin

error_out = ref - out_counter;

if (error_out == 3'b000)

begin

out_counter <= out_counter + 3'b001;

end

else

begin

out_counter <= out_counter + error_out;

end

end

endmodule

ROM code:

module stage4_ROM(CLK, out_counter, to_DAC);

input CLK;

input [2:0] out_counter;

output reg [15:0] to_DAC;

always @(out_counter)

begin

case (out_counter)

3'b000 : to_DAC = 16'h0000;

3'b001 : to_DAC = 16'h0046;

3'b010 : to_DAC = 16'h0064;

3'b011 : to_DAC = 16'h0046;

3'b100 : to_DAC = 16'h0000;

3'b101 : to_DAC = 16'h8046;

3'b110 : to_DAC = 16'h8064;

3'b111 : to_DAC = 16'h8046;

endcase

end

endmodule

TOP code:

module top_NCO(

input [2:0] samples_ref,

input CLK,

output [15:0] to_DAC

);

wire [2:0] net1;

stage2_phaseAccumulator stage01(.ref(samples_ref),.CLK(CLK),.out_ROM(net1));

stage4_ROM stage3(.CLK(CLK), .out_counter(net1), .to_DAC(to_DAC));

endmodule

TestBench:

module testbench_NCO();

reg [2:0] samples_ref;

reg CLK;

wire [15:0] out_ROM;

initial CLK = 1'b0;

always #25 CLK = ~CLK;

top_NCO t1(.samples_ref(samples_ref),.CLK(CLK),.to_DAC(out_ROM));

initial

begin

samples_ref <= 3'b000;

#50 samples_ref <= 3'b000;

#50 samples_ref <= 3'b001;

#50 samples_ref <= 3'b010;

#50 samples_ref <= 3'b011;

#50 samples_ref <= 3'b100;

#50 samples_ref <= 3'b101;

#50 samples_ref <= 3'b110;

#50 samples_ref <= 3'b111;

#50 samples_ref <= 3'b011;

#50 samples_ref <= 3'b100;

#50 samples_ref <= 3'b101;

#50 samples_ref <= 3'b110;

#50 samples_ref <= 3'b111;

#50 samples_ref <= 3'b000;

#50 samples_ref <= 3'b001;

#50 samples_ref <= 3'b010;

#50 samples_ref <= 3'b011;

#50 samples_ref <= 3'b100;

#50 samples_ref <= 3'b101;

#50 samples_ref <= 3'b110;

#50 samples_ref <= 3'b111;

#450 $finish;

end

initial

$monitor ("samples_ref=%d,out_ROM=%d", samples_ref, out_ROM);

endmodule

WAVE FORMS:

TOP:

0 comments:

Post a Comment